P板.com技術セミナー

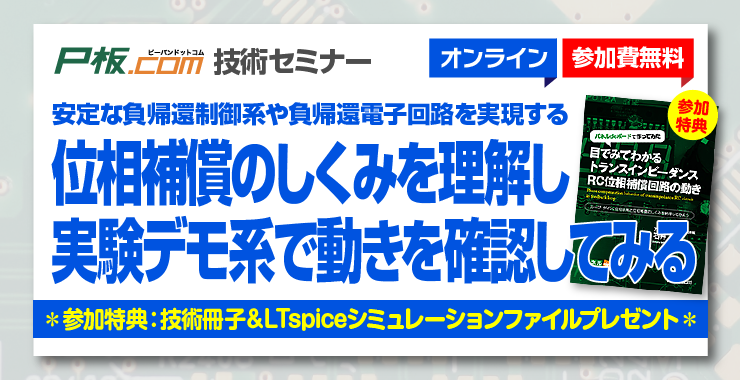

講演位相補償のしくみを理解し実験デモ系で動きを確認してみる

アナログ・デバイセズ株式会社 石井 聡 氏を講師に迎え、負帰還回路の安定性を示すループ・ゲインと位相余裕、そしてトランスインピーダンスRC位相補償回路の動作をわかりやすく解説いただきます。

位相補償回路について、実際に位相余裕と位相補償を確認できる基板を作成し、その動作のようすを測定した結果をご紹介します。なお単なる結果測定だけでなく、はじめは負帰還を安定化させる理論的なしくみから解説していただきます。

開催概要

| オンライン | |

|---|---|

| 日時・申込 | |

| 参加費 | 無料 |

| 定員 | 100名 |

| 準備するもの | インターネット環境 Zoomが利用可能な環境 |

| 会場 |

Zoomを使ってセミナーを行います。(通信テスト:https://zoom.us/test) オンラインセミナー参加方法 https://www.p-ban.com/others/online_seminar_beginner.html#online_flow |

| 備考 | Zoomは、事前にインストールしてください。初期設定に5分ほどの時間を要します。 お申し込み時のメールアドレスは、Zoomサインインで使用するものと同一でお願いします。 技術セミナー開催前日までに「招待リンク」を送付します。 当日は、招待リンクをクリックすると参加できます。 |

プログラム

| 14:00~14:05(5分) 本日のセミナーの流れ |

| 14:05~14:20(15分) P板.com会社サービス説明 |

| 14:20~15:40(80分) 講演 |

| 15:40~16:00(20分) 質疑応答 |

※プログラム内容等は、都合により予告なく変更することがございます。ご了承ください。

アナログ・デバイセズ株式会社

- 石井 聡 氏

-

1963年千葉県生まれ。1985年第1級無線技術士合格。1986年東京農工大学電気工学科卒業、同年電子機器メーカ入社、 長く電子回路設計業務に従事。

1994年技術士(電気・電子部門)合格。2002年横浜国立大学大学院博士課程後期 (電子情報工学専攻・社会人特別選抜)修了。博士(工学)。

2009年アナログ・デバイセズ株式会社入社。2018年中小企業診断士登録。 現在、デジタルデマンドジェネレーショングループ・技術戦略・シニアテクノロジスト。

デジタル回路(FPGAやASIC)からアナログ、 高周波回路まで多岐の電子回路の設計開発を経験。また、外部団体主催セミナーの講師を多数務める。アナログ・デバイセズでは「一緒に学ぼう!石井聡の回路設計WEBラボ」で多数の技術資料を公開。トランジスタ技術誌 2020年8月号より「Gbps超ハイスピード・プリント基板設計教科書」を連載執筆中。

「アナログ・デバイセズ株式会社」ホームページ>

「一緒に学ぼう!石井聡の回路設計WEBラボ」」ホームページ>