【プリント基板製造サービス】特性インピーダンス制御基板

P板.comでは特性インピーダンス制御の必要性を重視し、高い精度で制御可能な特性インピーダンス制御基板をご提供しております。

特性インピーダンス制御の必要性

半導体の信号入出力は高速化しています。

高速な電気信号がプリント基板の信号配線を伝わる時、インピーダンス(交流抵抗)が異なるところで電気信号が反射し、信号の波形が乱れ、半導体の誤動作につながります。

例えば、デジタル信号の「1(いち)0(ゼロ)」の並びを1周期として、DDR2メモリ・インタフェースでは最大266MHz、PCI Expressは1.25GHzです。

この反射を抑えるため、ドライバー(送り側)半導体とレシーバー(受け側)半導体との間の接続方法は、抵抗を挿入する位置によって、直列終端、並列終端、これらの併用などがあります。

全ての場合で、プリント基板の配線の特性インピーダンス制御が必要となります。

なお、プリント基板の配線の特性インピーダンスは、2種類の半導体間の信号伝送方式(1つの電気信号を伝えるために1本の配線を使用するシングルエンド伝送方式と、2本の配線を使う差動伝送方式)に対して、それぞれシングルエンド・インピーダンス(略してZo)、差動インピーダンス(略してZdiff)と呼ばれています。

シングルエンド伝送方式では、およそ100MHz以上でシングルエンド・インピーダンスの制御が重要になり、シングルエンド・インピーダンスの値としては50~65Ωが選ばれます。

差動伝送方式では400MHz以上になると差動インピーダンス制御が求められるようになり、差動インピーダンスの値は90~120Ωが一般的に選ばれています。

例として、高速なFPGAをドライバーとし、DDR2メモリがレシーバーの直列終端型1対1接続で、プリント基板の配線の長さが5cmの電気接続について、配線のシングルエンド・インピーダンスが適正な場合(50Ω)と高過ぎる場合(96Ω)の100MHzと166MHzにおけるDDR2の受信波形をシミュレーションした結果(図1)をご覧ください。

図1 シングルエンド・インピーダンス(Zo)制御のシミュレーション結果

配線の特性インピーダンスが適正な場合は、きれいな信号波形ですが、高過ぎるときはオーバーシュートやアンダーシュートのある乱れた波形になります。

また、50Ω終端系の高速FPGA間の2.5Gbps(1.25GHz)差動信号伝送で、プリント基板の差動配線長が10cm、この差動配線の差動インピーダンスが適正な場合(100Ω)と低過ぎる場合(60Ω)について、受信波形をシミュレーションした結果(図2)をご覧ください。

図2 差動インピーダンス(Zdiff)制御のシミュレーション結果

配線の特性インピーダンスが適正な場合は、きれいな信号波形ですが、低過ぎるときはジッタやノイズが増加し、波形が劣化します。

上記から、高速な信号が入出力する半導体を使うときは、プリント基板の配線の特性インピーダンス制御が必要となることがわかります。

テストクーポンの納品可能

P板.comの特性インピーダンス制御基板製造サービスでは、プリント基板の配線における特性インピーダンスを、±10%の精度で制御したプリント基板をご提供しています。 また、特性インピーダンス検査用「テストクーポン」にて、TDR法を用いた抜き取り検査を行っており、ご希望に応じて「テストクーポン」を製品と共に納品することや、「テストクーポン」の特性インピーダンス実測値を検査成績表としてご提出することも可能です。

- インピーダンステストクーポン+当該レポート一式 15,600円

- インピーダンスレポートのみ 7,800円

*ご要望の場合はお客様指示欄へ記載をお願い致します。

シングルエンド・インピーダンス(Z0)測定用テストクーポン(サンプル)

差動インピーダンス(Zdiff)測定用テストクーポン(サンプル)

特性インピーダンスの実測風景

特性インピーダンス制御を必要とするパターン設計手順

- 使用する半導体のアプリケーションノートに記載の特性インピーダンス値を確認します。記載が無ければ、プレ波形シミュレーションを行って特性インピーダンスの最適値を確認してください。

- シングル・差動インピーダンスそれぞれの値に対応した設計仕様(=配線幅と配線間隙)を、製造基準書(PDF形式)の層構成に基づき、対象となる配線のパターン設計を行ってください。

特性インピーダンスコントロール配線専用にアパーチャ(Dコード)を設定し、別途指示書に特性インピーダンスの指定値をご記載ください。

指示例

- 6層のアパーチャD307の配線に、シングルエンド50Ωのインピーダンス制御を行う。

⇒*Zo L6、50ohm on D307 - 8層のアパーチャD302の配線に、差動100Ωのインピーダンス制御を行う。

⇒*Zdiff L8,100ohm,on D302,L/S=0.15/0.15mm

※L/Sとは、パターンの配線幅(L)と間隔(S)を指します。

ご利用方法

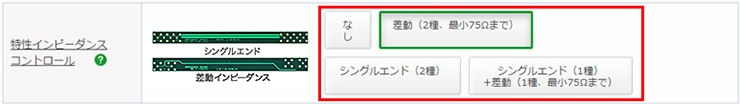

見積条件入力の「特性インピーダンス」でいずれかの項目をご選択ください。

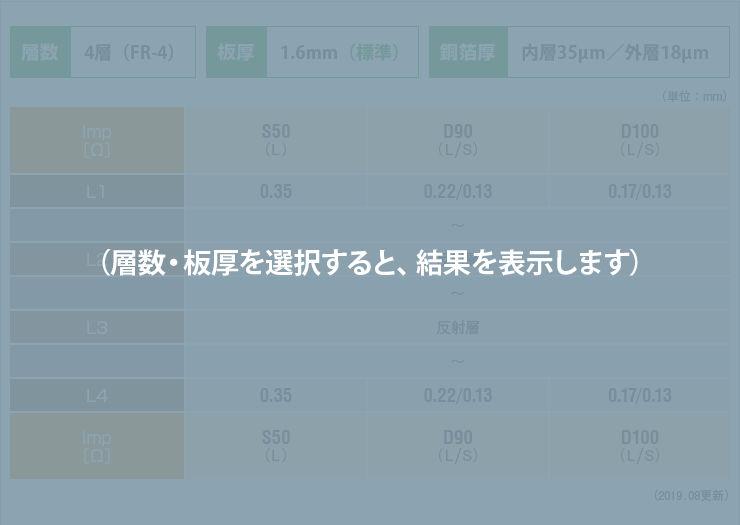

特性インピーダンスコントロール表

P板.com で特性インピーダンスコントロールが必要な基板を製作する場合は、下表の「線幅と間隙(以下、L/S)」をご参照の上、アートワーク設計をすすめてください。なお、製造工場で下表の数値を補正します。そのため、仕上がり値は、下表とは若干異なります。

選択項目

- FR-4

- 4層

- 6層

- 8層

- 1.6mm(標準)

- 0.8mm

- 1.0mm

- 2.0mm

※上記以外の条件をご希望の場合は、お問合せください。

※ご希望の線幅、間隙がある方は、お問い合わせフォームよりご相談ください。

※特性インピーダンスコントロール値は、略称で記載しておりますのでご注意ください。

・S50Ω︓シングルエンド・インピーダンス 50Ω

・D90Ω︓差動インピーダンス 90Ω

・D100Ω︓差動インピーダンス 100Ω